## Internetpress®

## MSP430 Microcontroller Engineering Guide

# **Getting Started**

### By Tomislav N. Krnich

B. Sc. in Physics

A book about the basic knowledge you need to have for developing programs for the MSP430. It is written in a bright, clear, and down-to-earth language for hobbyists, inventors, technicians, engineers, and product managers. It begins with presenting the MSP430's basic set of systems, their purposes, and how it starts, runs, goes to sleep, interrupted from sleep, performs work, and then goes back to sleep. Focus is on code and program development: accessing registers, the basic approach for developing a program, a programming reference model for getting oriented, the two basic patterns of program development, the most common programming routines and practices, the various types of input interruption signals which tell this microcontroller which interrupt service routine to use for carrying out work and producing output signals, and how to write the code for those routines. It is fully illustrated, indexed, and presents numerous programming examples. Included are many helpful tips. Ideal for self-paced, individualized learning. All examples are written in the C Programming Language.

## MSP430 Microcontroller Engineering Guide

## **Getting Started**

By Tomislav N. Krnich B.Sc. in Physics

Written, illustrated, edited, printed, bound, and published by the author.

TOMISLAV N. KRNICH (1961-) was born in Canada and then immigrated to the United States of America where he earned a Bachelors of Science degree in Physics with a minor in U.S. National Security Policy from Georgia State University. He has worked in the civil and defense aviation industries as an engineer, and in the telecom-munications, internet, information systems, and automotive industries as a solution architect, systems analyst, and technical writer. Embedded computing systems are one of his special interests.

Internetpress, Los Gatos, California 95032 http://internetpress.com © 2022 by Tomislav N. Krnich All rights reserved. Published August 2022

The author is grateful for your purchase. Please obey international copyright laws since the sale of this book provides an income for the author. Producing copies of this book for distribution is not permitted. Only the author has that right. You may contact the author through e-mail at the author book.

ISBN (vol 1): 978-0-9985736-0-1 (paperback)

- 81 Program Examples Written in the C Programming Language

- 90 Diagrams

- 29 Chapters

- Includes a Comprehensive Index

This book was produced in the United States of America.

While every precaution has been taken in the preparation of this book, the author assumes no responsibility for errors or omissions, or for damages resulting from the use of the information contained in this book.

Internetpress<sup>®</sup> is a registered trademark that is owned by the author.

This book is printed on acid free paper.

#### Contents

| 1 | Introduction                                                             | 1  |

|---|--------------------------------------------------------------------------|----|

|   | Data Processing as the Highest View of Handling Digital Data             |    |

|   | Microcontrollers are Built of System Modules and Peripheral Modules      |    |

|   | The Historical Emergence of the Microcontroller                          | 2  |

|   | Appearance of the MSP430 Microcontroller                                 | 3  |

|   | Why use the MSP430?                                                      | 3  |

|   | Purpose of this Book                                                     |    |

|   | Firmware is the Program of Instructions We Develop for a Microcontroller | 4  |

|   | Bits, Bytes, and the Native Word are the Basic Units of Data             |    |

|   | How the Microcontroller Views Data                                       | 5  |

|   | The MSP430 is Offered with Two Types of Processors: CPU and the CPUX     | 6  |

|   | How We [as Developers] may View and Express Data                         | 6  |

|   | Registers are Used for Configuring and Controlling the Microcontroller   | 6  |

|   | Main Memory Registers                                                    | 7  |

|   | What is a Main Memory Register used for?                                 | 8  |

|   | CPU Registers                                                            | 8  |

|   | Summary                                                                  |    |

|   |                                                                          |    |

| 2 | Visualizing How the MSP430 Operates                                      | 11 |

| - | Basic View                                                               |    |

|   | Power-up View                                                            |    |

|   | Event-Driven Views                                                       |    |

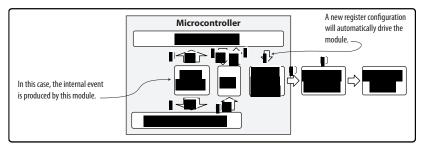

|   | View of an Internally Occurring Event                                    |    |

|   | Steps 1 and 2                                                            |    |

|   | CPU Interrupt System Behavior                                            | 14 |

|   | Step 3                                                                   |    |

|   | Steps 4, 5, 6, and 7                                                     |    |

|   | C, Assembly, and the Final ISR Instruction                               | 15 |

|   | Step 8                                                                   |    |

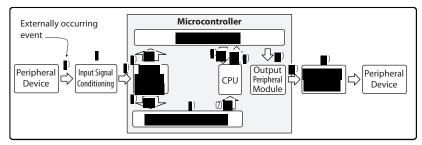

|   | View of an Externally Occurring Event                                    |    |

|   | Steps 1 and 2                                                            |    |

|   | Steps 3, 4, and 5                                                        | 17 |

|   | Steps 6 and 7                                                            | 17 |

|   | Steps 8, 9, 10, and 11                                                   | 17 |

|   | Step 12                                                                  | 17 |

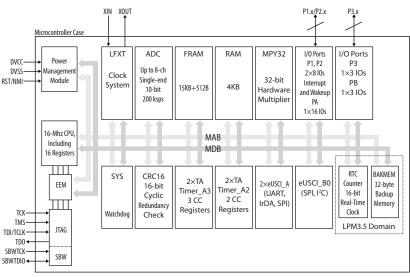

|   | Functional Block Diagram View                                            | 17 |

|   | Memory Modules                                                           | 18 |

|   | Memory Buses                                                             |    |

|   | Power Management Module                                                  |    |

|   | CPU, EEM, JTAG, and SBW Modules                                          |    |

|   | Clock System Module                                                      |    |

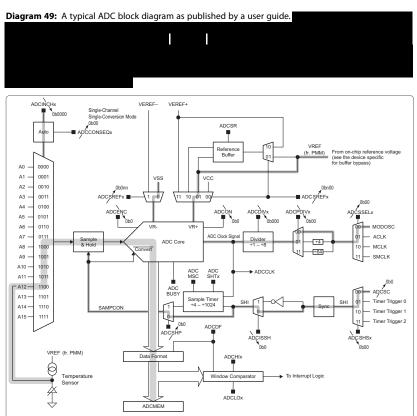

|   | ADC Module                                                               | 21 |

|   | MPY32 Module                                                             | 22 |

|   | I/O Ports                                                                | 22 |

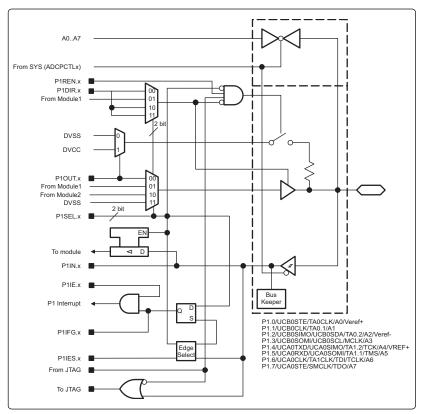

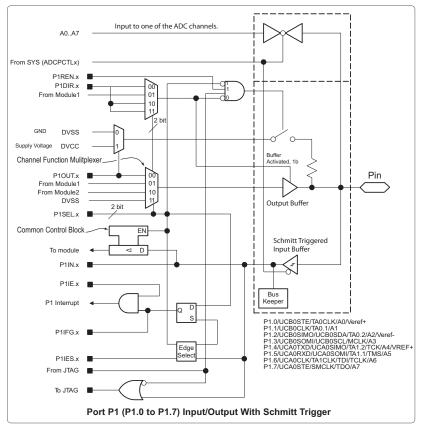

|   | Digital I/O Module                                                       | 24 |

|   | SYS Module                                                               | 24 |

|   | CRC16 Module                                                             |    |

|   | Timer Modules                                                            | 25 |

|   | continuation of the Functional Block Diagram View<br>Serving as a Frequency Dependent Timer | 26         |

|---|---------------------------------------------------------------------------------------------|------------|

|   | Serving as a Frequency Independent Counter                                                  |            |

|   | Serving as a Module for Measuring Rates                                                     |            |

|   | Serving as a Module for Producing PWM Voltage Signals                                       |            |

|   | How the Functional Diagram Describes the Timer Module                                       |            |

|   | eUSCI Module                                                                                |            |

|   | LPM3.5 Domain                                                                               |            |

|   | RTC Counter Module                                                                          |            |

|   | BAKMEM Module                                                                               |            |

|   | Pin Designation View                                                                        |            |

|   | Module Functional View                                                                      |            |

|   |                                                                                             | . 52       |

| 3 | Visualizing the Main Memory                                                                 |            |

|   | Main Memory Structure                                                                       |            |

|   | CPU Memory Structure                                                                        |            |

|   | Introduction to Register Tables                                                             | . 37       |

| 4 | The Reset System and its Subsystems                                                         | 39         |

| • | Power-Up                                                                                    |            |

|   | Reset                                                                                       |            |

|   | The BOR, POR, and PUC Sequence                                                              |            |

|   | Register Table Bitfields                                                                    |            |

|   | Reset Signals                                                                               |            |

|   | BOR Signals                                                                                 | . 40       |

|   | False BOR Signals                                                                           | . 41       |

|   | POR Signals                                                                                 | . 41       |

|   | PUC Signals                                                                                 | . 41       |

| 5 | How to Read and Use the Register Tables                                                     | 13         |

| 5 | The Conventional Register Table                                                             |            |

|   | Register Variable and Register Name                                                         | 43         |

|   | Register Variable                                                                           |            |

|   | Opening the Header File where the Register Variables are Declared                           |            |

|   | Register Bitfields                                                                          |            |

|   | Bitfield Mask                                                                               |            |

|   | Bitfield Mask Suffix                                                                        |            |

|   | The Standard Bits                                                                           |            |

|   | Register Bit Accessibility and Initial Condition                                            |            |

|   | Bitfield Descriptions                                                                       |            |

|   | Interrupt System Bitfields                                                                  | . 40<br>49 |

|   | Using a Register Table and Functional View to Help Develop Code                             |            |

|   | Distinguishing between a Digital I/O Module and Port                                        |            |

|   | Digital I/O Module                                                                          |            |

|   | Port                                                                                        |            |

|   | Port Register Tables                                                                        |            |

|   | Port Channels, Port Register Bitfields, and Port Register Bitfield Masks                    |            |

|   | First Type of Port Register Table                                                           |            |

|   | Second Type of Port Register Table                                                          |            |

|   | Third Type of Port Register Table                                                           |            |

|   | vi 0                                                                                        |            |

| 6  | Code Composer Studio Usage Tips                                     |      |

|----|---------------------------------------------------------------------|------|

|    | Forcing the CCS Debugger to Step through Each Instruction           |      |

|    | Configuring the Variables View for a Different Numbering Format     | 60   |

|    |                                                                     |      |

| 7  | How to Write into a Register                                        | 61   |

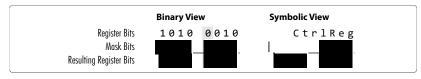

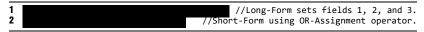

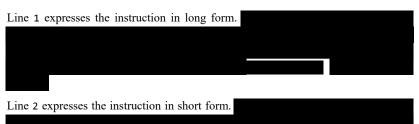

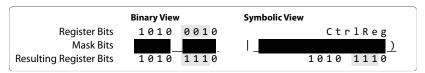

|    | Our Model Register                                                  |      |

|    | Masking Concepts                                                    |      |

|    | Overview of the Setting, Clearing, and Toggling Operations          |      |

|    | Setting Bits in a Register                                          |      |

|    | Setting a Single Bit                                                |      |

|    | Combining Masks to Create a Single Mask                             |      |

|    |                                                                     |      |

|    | Setting Multiple Bits                                               |      |

|    | Clearing Bits in a Register                                         |      |

|    | Clearing a Single Bit                                               |      |

|    | Clearing Multiple Bits                                              |      |

|    | Simultaneously Setting and Clearing Bits in a Register              |      |

|    | Toggling Bits in a Register                                         | 70   |

|    | Toggling a Single Bit                                               | 70   |

|    | Toggling Multiple Bits                                              | 71   |

|    | Just Simply Writing a Number into a Register                        | 71   |

|    | Writing into Password Protected Registers                           |      |

|    | 6 6                                                                 |      |

| 0  |                                                                     | 75   |

| 8  | How to Declare a Storage Variable                                   | . /3 |

|    | A Description for the Storage Variable                              |      |

|    | Declaring Storage Variables                                         | . 76 |

|    |                                                                     |      |

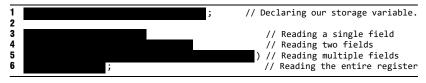

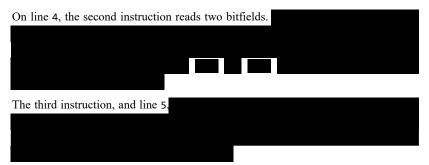

| 9  | How to Read a Register                                              | . 77 |

|    | The Process                                                         | . 77 |

|    | The Code                                                            | 77   |

|    |                                                                     |      |

| 10 | Background for Testing the Contents of a Register                   | 70   |

| 10 | Dackground for festing the Contents of a Register                   | . 79 |

|    | Integer Constants                                                   |      |

|    | The MSP430 Relaxed Compiler                                         |      |

|    | Using Binary Notation                                               |      |

|    | Enabling CCS Support for GCC Extensions                             | 80   |

|    |                                                                     |      |

| 11 | How to Test the Contents of a Register                              | 81   |

|    | The Process                                                         |      |

|    | The Code                                                            |      |

|    |                                                                     | 01   |

|    |                                                                     |      |

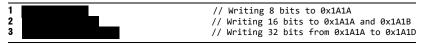

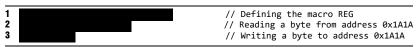

| 12 | How to use a Pointer to Read and Write into Main Memory             |      |

|    | Pointer and Pointer Variable                                        |      |

|    | Indirection Operator                                                | 83   |

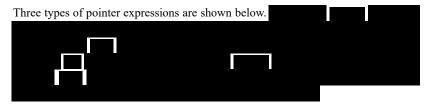

|    | Converting an Address Number into a Pointer: the Pointer Expression | 84   |

|    | Declaring a Pointer Variable                                        | 85   |

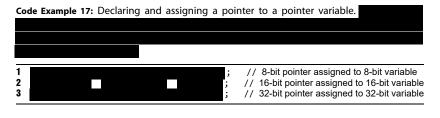

|    | Declaring a Pointer and Assigning it to a Pointer Variable          |      |

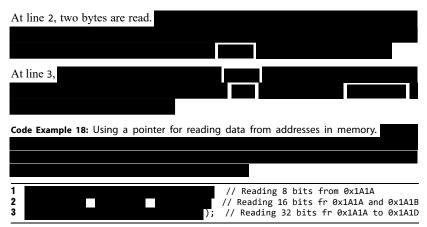

|    | Reading Data                                                        |      |

|    | Using a Pointer                                                     |      |

|    |                                                                     |      |

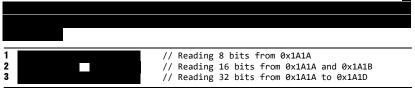

|    | Using a Pointer Variable                                            | - 27 |

|    | Using a Pointer Variable                                            |      |

|    | Using a Pointer Variable                                            | 87   |

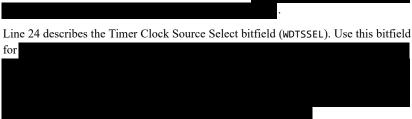

| 13 | Watchdog Timer and Putting it on Hold                                                                                     | . 89     |

|----|---------------------------------------------------------------------------------------------------------------------------|----------|

|    | Purpose                                                                                                                   |          |

|    | Basic Operation                                                                                                           | . 89     |

|    | Interval Reset Instruction                                                                                                |          |

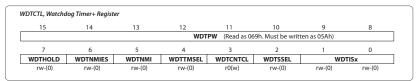

|    | Watchdog Control Register Table                                                                                           |          |

|    | Stopping the Watchdog Timer                                                                                               |          |

|    | Writing an Active Watchdog Timer Handler                                                                                  |          |

|    | Stopping the Watchdog Timer during the Boot Process                                                                       |          |

|    | Using Boot Hook Functions to Stop the Watchdog and Execute other Instructions .                                           |          |

|    | Using the _system_pre_init() function                                                                                     |          |

|    | Using the system post cinit() function                                                                                    |          |

|    | Reading the Watchdog Timer Register                                                                                       |          |

|    |                                                                                                                           | . 90     |

| 14 | main() Function                                                                                                           | . 99     |

|    | Purpose                                                                                                                   |          |

|    | How the main() Function is Called                                                                                         | . 99     |

|    | Syntax and Format for a C Language Function                                                                               | . 99     |

|    | The Two Standard Syntaxes for the main() Function                                                                         | 100      |

|    | First Syntax and Format                                                                                                   |          |

|    | main() is Void of Parameters                                                                                              |          |

|    | The return Statement                                                                                                      |          |

|    | Second Syntax and Format                                                                                                  |          |

|    |                                                                                                                           | 101      |

| 15 | Program Development Nomenclature                                                                                          | 103      |

|    | Routines                                                                                                                  | 103      |

|    | Subroutines                                                                                                               | 103      |

|    | Block of Instructions                                                                                                     |          |

|    | Logic Circuits as Routines and Subroutines                                                                                | 103      |

|    | Service                                                                                                                   | 103      |

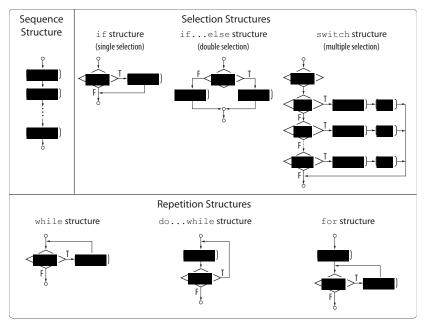

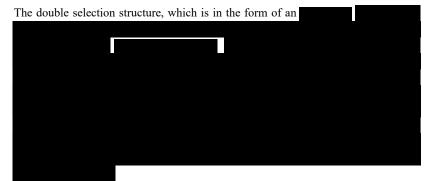

| 16 | Structures for Program Development                                                                                        | 105      |

| 10 |                                                                                                                           |          |

|    |                                                                                                                           |          |

|    |                                                                                                                           |          |

|    | Repetition Structures                                                                                                     | 100      |

| 17 | Basic Approach for Developing a Microcontroller Solution                                                                  |          |

|    | Task 1: Conceptualize the Problem and its Solution                                                                        |          |

|    | Task 2: Design the Power Supply Interface Circuit                                                                         |          |

|    | Task 3: Design the Signal Input Interface Circuit                                                                         | 107      |

|    | Task 4: Develop Instructions which Configure the Signal Input Path                                                        | 107      |

|    | Task 5: Develop Instructions which Configure the Input Module                                                             |          |

|    | Task 6: Develop Instructions which Make Decisions                                                                         |          |

|    |                                                                                                                           |          |

|    |                                                                                                                           |          |

|    |                                                                                                                           |          |

|    | Task 10: Design the Signal Output Interface Circuit                                                                       |          |

| 16 | Structures for Program Development.         Sequence Structure         Selection Structures         Repetition Structures | 1(<br>1( |

|    |                                                                                                                           |          |

| 17 |                                                                                                                           |          |

|    |                                                                                                                           |          |

|    |                                                                                                                           |          |

|    |                                                                                                                           |          |

|    |                                                                                                                           |          |

|    |                                                                                                                           |          |

|    | Task 7: Develop Instructions which Act on the Result of a Decision                                                        | 108      |

|    | Task 8: Develop Instructions which Configure the Output Module                                                            | 108      |

|    | Task 9: Develop Instructions which Configure the Signal Output Path                                                       |          |

|    |                                                                                                                           |          |

|    |                                                                                                                           |          |

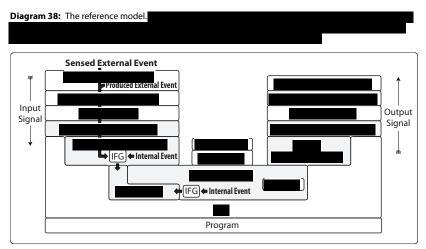

| 18 | MSP430 Reference Model                                 | 109 |

|----|--------------------------------------------------------|-----|

|    | Structural Overview                                    | 109 |

|    | Input Signal Stack                                     | 110 |

|    | Externally Occurring Events                            | 111 |

|    | Internally Occurring Events                            | 112 |

|    | Output Signal Stack                                    |     |

|    | Power Supply Stack                                     | 113 |

|    |                                                        |     |

| 19 | Patterns for Program Development                       | 115 |

|    | Repetitive-Driven Pattern of Program Development       |     |

|    | Configure and Setup Sequence                           |     |

|    | Watchdog Timer Handler                                 |     |

|    | Oscillator Settling Handler                            |     |

|    | Signal I/O Multiplexing                                |     |

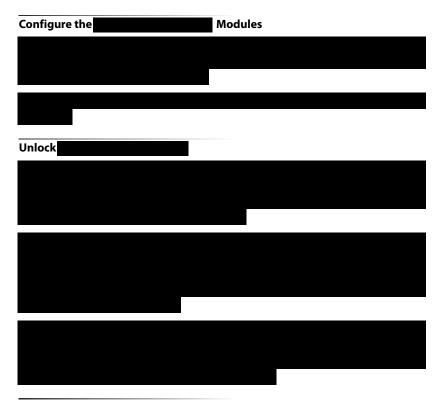

|    | Configure the System and Peripheral Modules            |     |

|    | Unlock Digital I/O Port Channels                       |     |

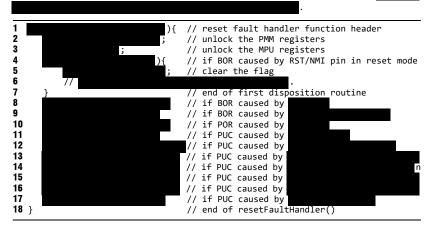

|    | Reset Fault Handler                                    |     |

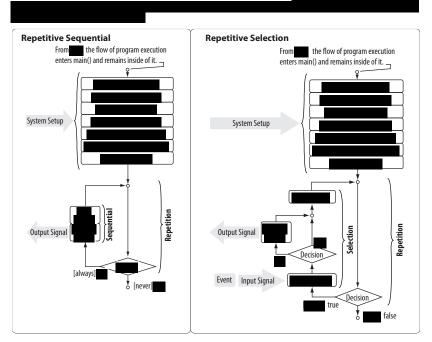

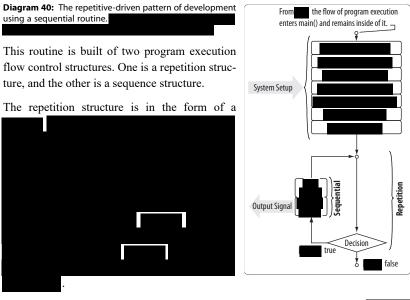

|    | The Repetitive Sequential Routine                      |     |

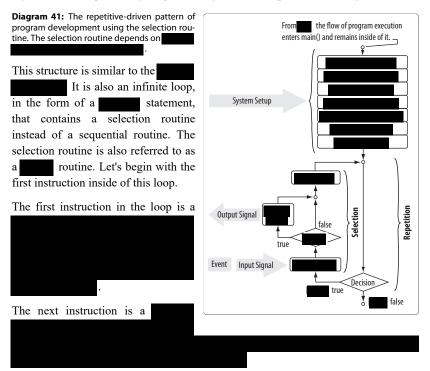

|    | The Repetitive Selection Routine                       |     |

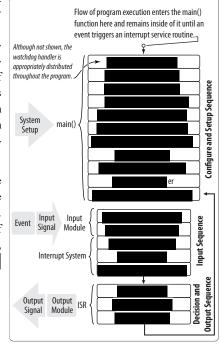

|    | Event-Driven Pattern of Program Development            |     |

|    | System Configuration and Setup Sequence                |     |

|    | Watchdog Timer Handler                                 |     |

|    | About the Next six Routines                            | 122 |

|    | Oscillator Settling Handler                            | 122 |

|    | Signal I/O Multiplexing                                |     |

|    | Configure the System and Peripheral Modules            | 122 |

|    | Unlock the Digital I/O Port Channels                   | 123 |

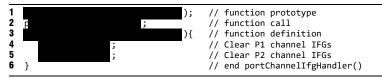

|    | Port Channel Interrupt Flag Handler                    | 123 |

|    | System Reset Fault Handler                             | 123 |

|    | Enable Maskable Interruptions                          | 124 |

|    | Volatile Data Handler                                  |     |

|    | Enter a Low Power Operating Mode                       | 125 |

|    | Input Signal Sequence                                  | 125 |

|    | Decision and Output Signal Sequence                    | 125 |

|    |                                                        |     |

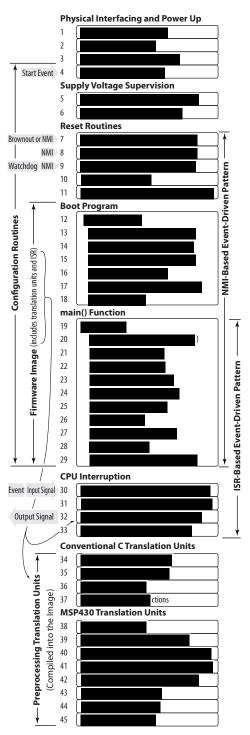

| 20 | Placing the Event-Driven Pattern into a Larger Context | 127 |

|    | Physical Interfacing and Power-Up                      |     |

|    | Supply Voltage Supervision                             |     |

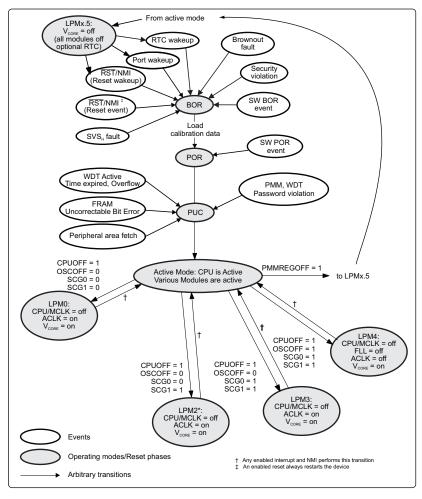

|    | Operating Mode Diagram                                 |     |

|    | Reset Routines                                         |     |

|    | Brownout Reset (BOR)                                   |     |

|    | Power-On Reset (POR)                                   |     |

|    | Power-Up Clear (PUC)                                   |     |

|    | MSP-BSL and boot.c                                     |     |

|    | MSP-BSL                                                |     |

|    | Boot Program                                           |     |

|    | Boot Program Execution                                 |     |

|    | Initializing the Program Execution Stack               |     |

|    | Initializing the Memory Protection Unit                |     |

|    | Execute a Pre-Initialization Function                  |     |

|    | Initialize Global Variables                            |     |

|    | Execute a Post Initialization Function                 |     |

|    | Call the main() Function                               | 142 |

|    | main() Function                                               |       |

|----|---------------------------------------------------------------|-------|

|    | CPU Interruption                                              |       |

|    | Preprocessing Translation Units                               |       |

|    | Conventional C Translation Units                              |       |

|    | #include Preprocessor Directives                              |       |

|    | #define Preprocessor Directives                               |       |

|    | Define Global Variables                                       |       |

|    | Define Conventional Functions                                 |       |

|    | MSP430 Translation Units                                      |       |

|    | #include <msp430.h></msp430.h>                                |       |

|    | #include Specialized MSP430 Library Headers                   |       |

|    | Define a Pre-initialization Boot Hook Function                |       |

|    | Define a Post initialization Boot Hook Function               |       |

|    | Define an Interrupt Service Routine (ISR)                     |       |

|    | Define #pragma Directives                                     | . 147 |

|    |                                                               |       |

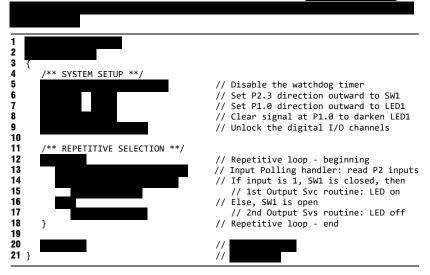

| 21 | Repetitive-Driven Programming Examples                        | . 149 |

|    | Development Tools                                             |       |

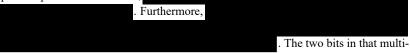

|    | Repetitive Sequential Pattern                                 |       |

|    | Pseudo Code Template                                          |       |

|    | Using a Repetitive Sequence to Produce an Output Signal       |       |

|    | Model Use Case                                                |       |

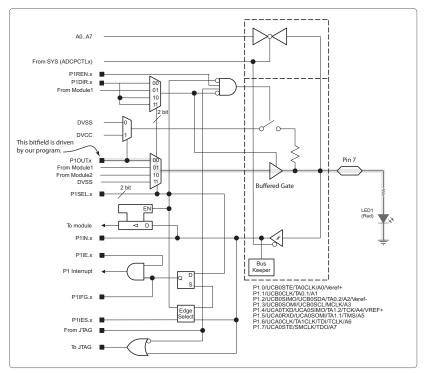

|    | Interfacing Circuit                                           |       |

|    | Output Signal Pathway                                         |       |

|    | The Program                                                   |       |

|    | Block of System Setup Instructions                            |       |

|    | Block of Repetitive Sequential Instructions                   |       |

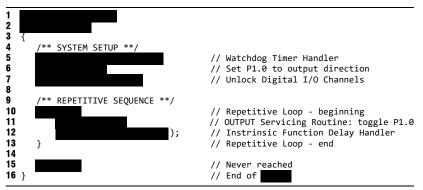

|    | Repetitive Selection Pattern                                  |       |

|    | Pseudo Code Template                                          |       |

|    | Using an External Input Signal for Selecting an Output Signal |       |

|    | Model Use Case                                                |       |

|    | Interfacing Circuits                                          |       |

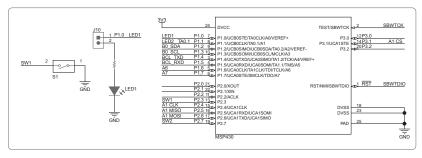

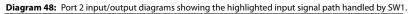

|    | Switch Circuit and Its Operation                              |       |

|    | First State Operation: Switch is Open                         |       |

|    | Second State Operation: Switch is Closed                      |       |

|    | LED Circuit                                                   |       |

|    | The Program                                                   |       |

|    | Block of System Setup Instructions                            |       |

|    | Block of Repetitive Selection Instructions                    |       |

|    | Using an Internal Input Signal for Selecting an Output Signal |       |

|    | Model Use Case                                                |       |

|    | Interfacing Circuits                                          |       |

|    | Input Interfacing Circuit                                     |       |

|    | Output Interfacing Circuits                                   |       |

|    | Signal Pathways                                               |       |

|    | Input Path from the Temperature Sensor                        |       |

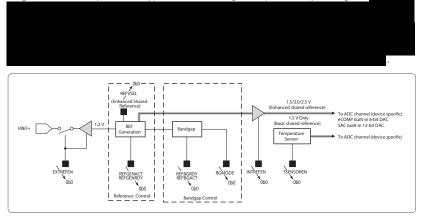

|    | PMM Section                                                   |       |

|    | ADC Section: Input Signal Multiplexing                        |       |

|    | ADC Control Signals                                           |       |

|    | Voltage Measurement Scale                                     |       |

|    | Clock Conversion Signal                                       |       |

|    | SAMPCON and SHI Signals                                       |       |

|    | ADCENC and ADCON Signals                                      |       |

|    | Output Paths to LED1 and LED2                                 |       |

|    |                                                               | 0/    |

| continuation of Using an Internal Input Signal for Selecting an Output Signal for Selecting an Output Signal |     |

|--------------------------------------------------------------------------------------------------------------|-----|

| The Program                                                                                                  |     |

| Block of System Setup Instructions                                                                           |     |

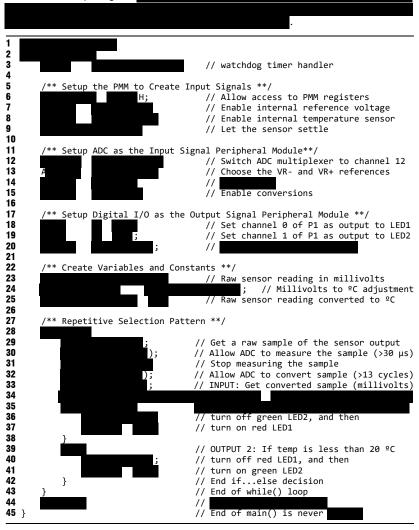

| Write a Watchdog Timer Handler                                                                               |     |

| Setup the Sensor to Create Input Signals                                                                     |     |

| Setup the ADC as the Input Signal Peripheral Module                                                          | 169 |

| Setup the Digital I/O as the Output Signal Peripheral Module                                                 | 170 |

| Declare Variables and Constants                                                                              | 170 |

| Block of Repetitive Selection Instructions                                                                   | 172 |

|                                                                                                              |     |

| 22 Event-Driven Programming Routines and Practices                                                           | 175 |

| Boot Initialization                                                                                          |     |

| Pre-Initialization                                                                                           | 175 |

| Post Initialization                                                                                          | 175 |

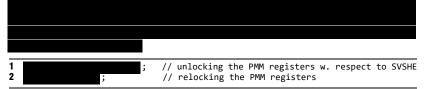

| Manipulating Bits in Password Protected Registers                                                            | 176 |

| Password that Protects a Single Register                                                                     | 176 |

| Password that Protects a Set of Registers                                                                    | 177 |

| Watchdog Timer Handlers                                                                                      | 178 |

| Placing the Watchdog on Hold                                                                                 |     |

| Using Watchdog Mode                                                                                          |     |

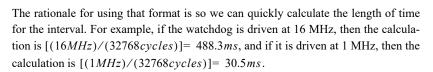

| The Counter Interval                                                                                         | 179 |

| The Pattern                                                                                                  | 179 |

| The Code Examples                                                                                            | 180 |

| Oscillator Settling Handler                                                                                  | 182 |

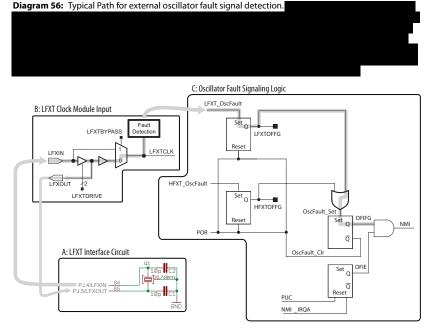

| Signal Path from an External Oscillator to the Fault Detector                                                |     |

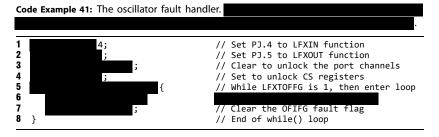

| Code Example for the Oscillator Fault Handler                                                                | 184 |

| Configuring a Port Channel                                                                                   |     |

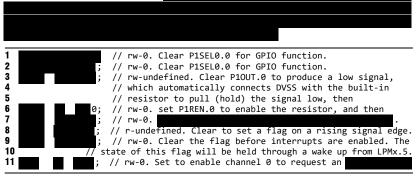

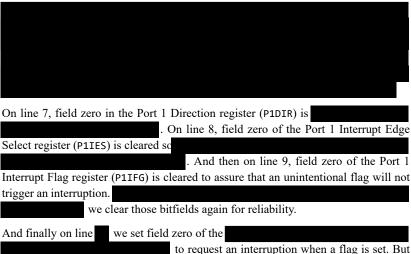

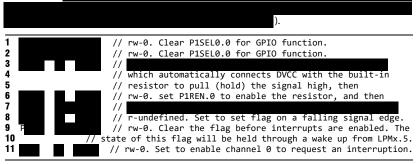

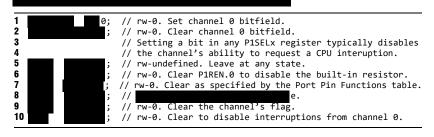

| Configuring as a GPIO Input for Sensing a Signal Changing from Low to High .                                 | 190 |

| Configuring as a GPIO Input for Sensing a Signal Changing from High to Low .                                 | 191 |

| Configuring a Channel as a Non-GPIO Function                                                                 | 192 |

| Configuring a Port Channel as Unused                                                                         | 197 |

| Accessing Protected Registers                                                                                | 197 |

| Watchdog Registers                                                                                           | 197 |

| Power Management Module Registers                                                                            | 197 |

| Clock System Registers                                                                                       | 198 |

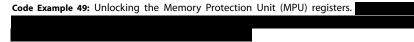

| Memory Protection Unit (MPU) Registers                                                                       | 198 |

| Configuring Unused Port Channels                                                                             |     |

| Code Example for Putting a Port Channel into a High Impedance State                                          |     |

| Unlocking Modules & Digital Port Channels which are in the LPMx.5 Domain                                     |     |

| Port Channel Interrupt Flag Handler                                                                          |     |

| Clearing a Port Channel Flag from Inside of an ISR                                                           |     |

| Determining the Source of an Interrupt Flag                                                                  |     |

| Interrupt Vector                                                                                             |     |

| Flow of Execution from a Set Flag to an ISR or an RFH                                                        |     |

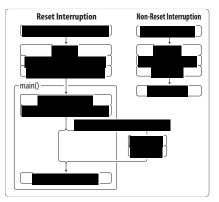

| Basic Flow for the Non-Maskable and Maskable Interruptions                                                   |     |

| Basic Flow for the Reset Interruption                                                                        |     |

| Flag to Routine Relationships                                                                                |     |

| Flag to Reset Fault Handler (RFH) Relationship                                                               |     |

| Flag to ISR Relationships                                                                                    |     |

| Flag Determining Code Examples                                                                               |     |

| Using the if() Statement                                                                                     |     |

| Using the switch() Statement                                                                                 |     |

| Theeven_in_range() Function                                                                                  | 208 |

|    | continuation of Using the switch() Statement                             |       |

|----|--------------------------------------------------------------------------|-------|

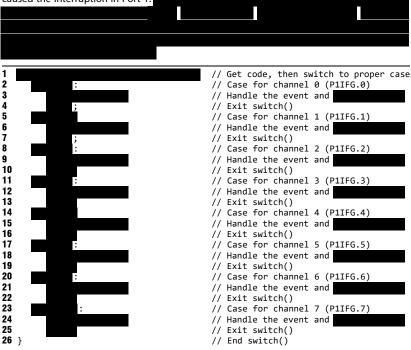

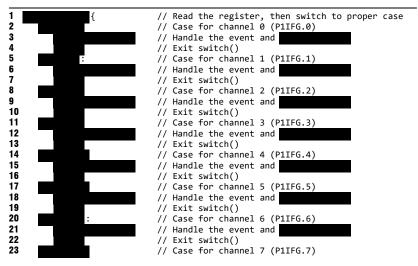

|    | Code Example for using the switch() to Determine which Flag is Set       | . 209 |

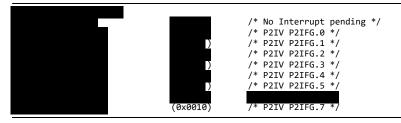

|    | The PxIV Register Table                                                  | . 209 |

|    | The switch() Code                                                        |       |

|    | Conventional Register Scenario                                           | . 211 |

|    | Enabling and Disabling Maskable Interruptions                            | . 212 |

|    | Unlocking and Locking FRAM                                               | . 213 |

|    | Review of Volatile and Non-Volatile Memory                               | . 213 |

|    | FRAM Access Control                                                      | . 213 |

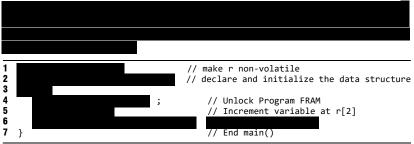

|    | Example for Unlocking and Locking FRAM                                   | . 214 |

|    | Register which Controls the FRAM                                         |       |

|    | Code Example                                                             | . 216 |

|    | Volatile Data Handler                                                    |       |

|    | Using the PERSISTENT() #pragma to Protect Volatile Data                  | . 218 |

|    | Code Example for Protecting a Single Variable                            | . 218 |

|    | Code Example for Protecting the Variables in an Array                    |       |

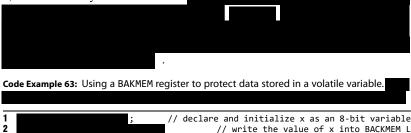

|    | Using the Backup Memory Registers                                        | . 220 |

|    | Determining How Much Memory is Consumed                                  | . 221 |

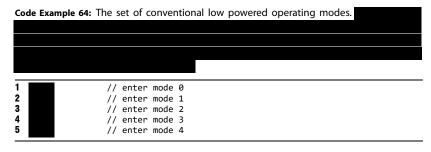

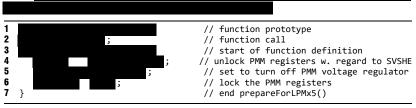

|    | Entering a Low Powered Operating Mode                                    |       |

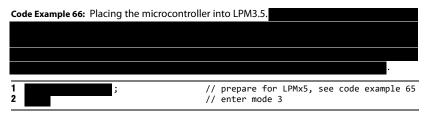

|    | Conventional Lower Powered Operating Modes                               |       |

|    | Fractional Lower Powered Modes (LPMx.5)                                  | . 223 |

|    | Delay Function                                                           | . 225 |

|    |                                                                          |       |

| 23 | Interrupt Handling and Interrupt Vectors                                 | . 227 |

|    | CPU Interruptions are Event-Driven                                       | . 227 |

|    | Event Monitoring Blocks                                                  | . 227 |

|    | Conventional Flag Registers and Interrupt Vector Registers               | . 227 |

|    | The Interrupt Service Routine and Vector                                 | . 228 |

|    | Interrupt Vectors                                                        | . 228 |

|    | Block of Interrupt Control Logic                                         | . 229 |

|    | Reset, Non-Maskable (NMI), and Maskable Types of Interruptions           | . 229 |

|    | How the Interruption is Processed                                        |       |

|    | Transfer of Program Execution to the ISR                                 | . 231 |

|    | Execution while inside of the ISR                                        | . 231 |

|    | Transfer of Program Execution from the ISR back to the Low Powered State | . 232 |

|    | Interrupt Prioritization                                                 | . 232 |

|    | Interrupt Compare Controller (ICC)                                       | . 233 |

|    |                                                                          |       |

| 24 | How to Determine which are the Multi-Flagged Vectors                     | . 235 |

|    | Determining which Vectors are Bound to More than one Flag                |       |

|    | Finding the Name of the Register where the Flag is Located               | . 235 |

|    |                                                                          |       |

| 25 | The Reset Interruption                                                   |       |

|    | Flow for the System Reset Interruption                                   | . 238 |

|    | The Reset Fault Handler (RFH)                                            |       |

|    | Reset Fault Handler Based on if() Statements                             |       |

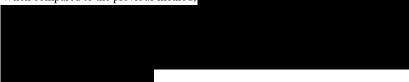

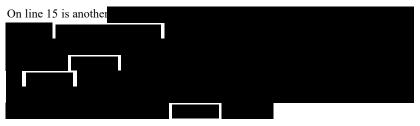

|    | Reset Fault Handler Based on a switch() Statement                        |       |

|    | Reset Caused by a Watchdog Timer Overflow                                | . 244 |

| 26 | How to Write an Interrupt Service Routine (ISR)                                | 245 |

|----|--------------------------------------------------------------------------------|-----|

|    | The Conventional ISR                                                           |     |

|    | Built-in Default Interrupt Service Routine (ISR)                               | 247 |

|    | Customized Default Interrupt Service Routine (ISR)                             | 248 |

|    |                                                                                |     |

| 27 | Non-Maskable Interruption (NMI)                                                |     |

|    | Flow for the Non-Maskable Interruption (NMI)                                   |     |

|    | Non-Maskable ISR Examples                                                      |     |

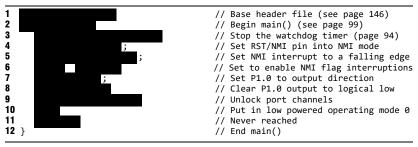

|    | main() Function for ISR Code Examples 76 and 77                                |     |

|    | Putting the RST/NMI Pin into NMI Mode                                          |     |

|    | Configuring P1.0 to Drive the LED                                              | 256 |

|    | Final Instructions for main()                                                  | 256 |

|    | ISR which uses the if() Selection Statement to Determine the NMI Flag          | 257 |

|    | The ISR's Behavior                                                             | 257 |

|    | Writing the ISR                                                                | 257 |

|    | Getting the Vector's Name                                                      | 257 |

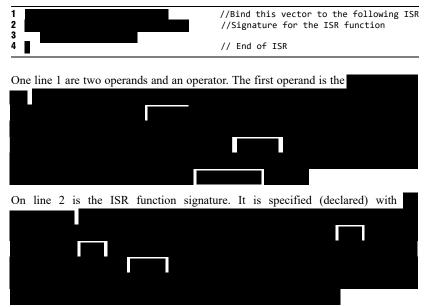

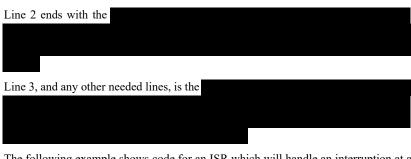

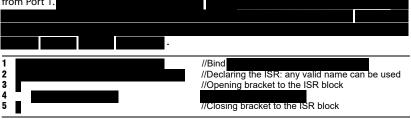

|    | Binding the Vector to the ISR                                                  | 258 |

|    | The ISR's Signature                                                            | 258 |

|    | The First if() Selection Statement                                             | 258 |

|    | The Second if() Selection Statement                                            |     |

|    | Returning the Flow of Execution Back to where it was Interrupted               |     |

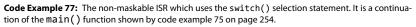

|    | ISR which uses the switch() Selection Statement to Determine the NMI Flag      |     |

|    | The ISR's Behavior                                                             |     |

|    | Writing the ISR                                                                |     |

|    | Getting the Vector's Name                                                      |     |

|    | Binding the Vector to the ISR                                                  |     |

|    | The ISR's Signature                                                            |     |

|    | Getting the IVR Register Variable and it Codes                                 |     |

|    | The switch() Statement                                                         |     |

|    | Returning the Flow of Execution Back to where it was Interrupted               |     |

|    | Retaining the riow of Execution Back to where it was interrupted               | 204 |

| 28 | Maskable Interruption                                                          | 265 |

|    | Flow for the Maskable Interruption                                             | 266 |

|    | About this Chapter's Examples                                                  | 268 |

|    | ISR using the if() Selection Statement to Determine which Maskable Flag is Set |     |

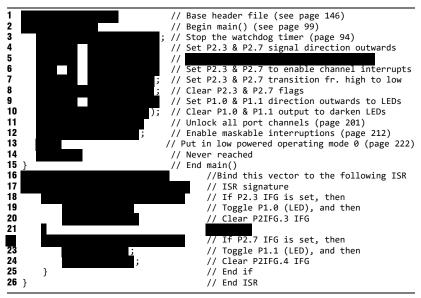

|    | The main() function                                                            | 270 |

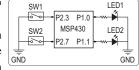

|    | Configuring P2.3 and P2.7 to Sense Input Signals                               | 270 |

|    | Configuring P1.0 and P1.1 to Produce Output Signals                            |     |

|    | Final Instructions for main()                                                  |     |

|    | The ISR's Behavior                                                             | 272 |

|    | Writing the ISR                                                                |     |

|    | Port Channel Flag Names                                                        |     |

|    | Getting the Interrupt Vector Name                                              |     |

|    | Binding the Vector to the ISR                                                  |     |

|    | The ISR's Signature                                                            |     |

|    | How Many if() selection Statements to Use                                      |     |

|    | The First if() Selection Statement                                             |     |

|    | The Second if() Selection Statement                                            |     |

|    | Returning the Flow of Execution Back to where it was Interrupted               |     |

|    | Returning the Flow of Execution Back to where it was interrupted               | 2/4 |

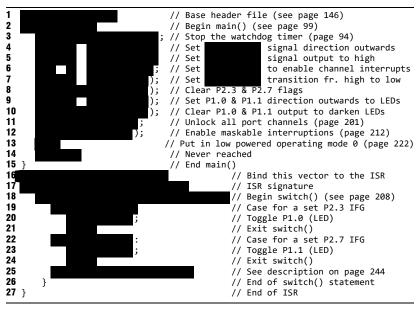

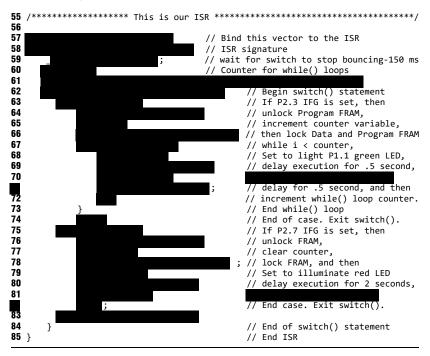

|     | ISR using the switch() Selection Statement to Determine which Maskable Flag is Set | . 274 |

|-----|------------------------------------------------------------------------------------|-------|

|     | The main() Function                                                                | . 274 |

|     | The ISR's Behavior                                                                 | . 275 |

|     | Writing the ISR                                                                    | . 275 |

|     | Getting the Port Channel Flag Names                                                | . 275 |

|     | Getting the Interrupt Vector Name                                                  | . 276 |

|     | Binding the Vector to the ISR                                                      | . 277 |

|     | The ISR's Signature                                                                | . 277 |

|     | How Many case selection Statements to Use                                          | . 277 |

|     | The First Case                                                                     | . 277 |

|     | The Second Case                                                                    | . 278 |

|     | Returning the Flow of Execution Back to where it was Interrupted                   | . 278 |

| -   |                                                                                    | 270   |

| 29  | ······································                                             |       |

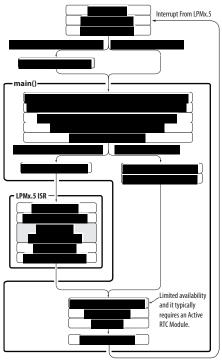

|     | Flow for the LPMx.5 Interruption                                                   |       |

|     | Flow for the LPMx.5 Interrupt Service Routine (ISR)                                |       |

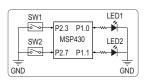

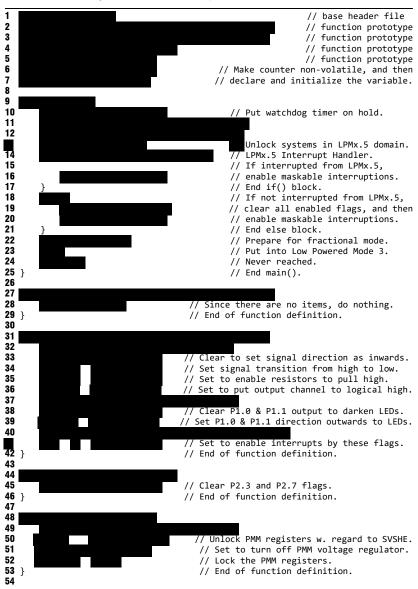

|     | Program Example                                                                    | . 285 |

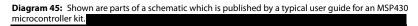

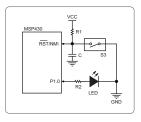

|     | Circuit Schematic for the Program                                                  | . 286 |

|     | How the Program Example Works                                                      | . 286 |

|     | Structure of the Program Example                                                   | . 287 |

|     | Program Example                                                                    | . 288 |

| Inc | dex                                                                                | . 293 |

The MSP430 microcontroller is typically used for monitoring and controlling devices, but it is not limited to just that type of work. It is a general purpose data processing machine, and such a machine is called a digital computer. It reads data from a device, it then processes the data to make decisions, and the results of those decisions produces data which then is used for controlling, driving, or communicating with a device. Furthermore, a single MSP430 is not limited to interacting with a single device. It can simultaneously handle many devices.

Data which flows into and out of the MSP430 are in the form of voltage signals which flow at low rates of amperes. The voltages range from to voltage volts of direct current (VDC). The amperes range from to about milliampere.

There are a very wide variety of devices which the MSP430 can monitor and control, and all those devices can produce and receive a wide variety of analog and digital voltage signals. Therefore, we can perceive the MSP430 as being a type of computer called a mixed signal processor. But not just a mixed signal processor, it is a stored program mixed signal processor. That means it will handle and produce many different types of analog and digital signals while under the control of a computer program.

Signals which enter the MSP430 are converted to binary numbers so the signals can be understood by it and processed, in other words, so decisions can be made. The results of the decisions are also in the form of and stored as binary numbers. The result of a decision is typically used for producing an output signal. Binary numbers, which form a decision, are then converted to the appropriate type of analog or digital output signal.

The binary numbers which are processed (meaning, analyzed, manipulated, and moved around inside of the microcontroller) are referred to as binary data or digital data. Electronic circuits which handle digital data are called digital logic circuits. The work carried out by such circuits is called data processing.

#### Data Processing as the Highest View of Handling Digital Data

Data processing involves computation and movement of digital data. The set of circuits which handle computation is called the arithmetic logic unit (ALU). The set of circuits which handle the movement of data, so the ALU can access it, is called control logic. The combination of these computation and movement circuits is called a data processing unit, and when built into a digital computer, they are called a central processing unit (CPU).

A CPU needs instructions in order to know where to get data, to know which computations to perform on the data, and where to put the resulting data. Those instructions

#### 2 Introduction

are in the form of a program which is loaded in the computer's memory. The CPU uses its control logic for locating the beginning of the program, and then sequentially reads and executes each instruction in the program. These steps are called the fetch and execute cycle. A CPU which is under the control of a program is called a micro-processor.

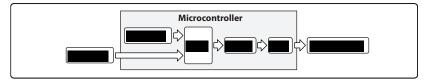

Besides fetching and executing instructions, the CPU control logic also handles the work needed for transferring data back into memory and for controlling blocks of digital logic circuits which support the microprocessor in specific ways. Those blocks are called modules. There are two types of modules: system modules and peripheral modules.

#### Microcontrollers are Built of System Modules and Peripheral Modules

A system module supports the overall operation of the CPU. For example, two essential types of system modules are called the clock module and the memory module. The clock provides a timing signal which the CPU uses for cycling though its fetch and execution cycles, and the memory module stores the program.

A peripheral module acts as a data interface in between the microprocessor and a device which the microcontroller is monitoring or controlling. In other words, it handles voltage signals coming from or going out to some type of device. The signals are called microprocessor input and output signals.

For data flowing into the microcontroller, the peripheral module converts input signals into digital data and then makes it available to the microprocessor by placing it in a specific location in memory. For data flowing out of the microcontroller, the module gets digital data from some specific location in memory, and then converts it to some type of voltage output signal. The output signal is in the form or type which can be accepted and used by the device. The device is referred to as a peripheral device, and such a device maybe in the form of a switch, relay, sensor, actuator, display, application specific integrated circuit (ASIC), or another microcontroller.

#### The Historical Emergence of the Microcontroller

During the middle 1960's, the ALU, control logic, and the peripheral modules were fabricated into separate silicon chips of integrated circuits to form a chip set. The individual chips had to be connected together with wires to form what was called back then a microcomputer. Although there were various technologies used for creating memory modules, memory was typically fabricated of toroidal magnets to form non-volatile program storage that was called magnetic core memory. Non-volatile means the program will not be lost after the computer is turned off. The Apollo space flight guidance computer was built of core memory.

Around 1970, the set of chips which formed the ALU and control logic were integrated into a single silicon chip that was called a one-chip microcomputer. This book will often refer to the ALU and control logic as the central processing unit (CPU) or microprocessor. Memory modules and peripheral modules, however, were still externally connected components. And it was around this time when memory began to be available as practical integrated circuits built on silicon. Peripheral modules made of integrated circuits also grew in sophistication.

During the middle 1970's, the memory module and the general purpose input and output peripheral module began to be integrated into the one-chip microcomputer. And during the 1980's, this type of one-chip microcomputer began to be called a microcontroller.

#### Appearance of the MSP430 Microcontroller

During 1992, Texas Instruments began to offer the MSP430, where MSP is an acronym for mixed signal processor. Mixed signal means that various types of input signals could be fed into it, and various types of output signals could be produced by it. That ability was created by integrating the microprocessor with a variety of specialized peripheral modules into a single integrated circuit. Since that time, Texas Instruments has continually improved the MSP430 microprocessor and also to continually develop different types of peripheral modules. Today, there are over four hundred different models of the MSP430, and the models branch out into families. Each model is distinguished by their unique set of system and peripheral modules.

#### Why use the MSP430?

Whatever can be done by a microcontroller can also be done with circuits built of ordinary discrete devices such as resistors, transistors, capacitors, diodes, and wires. And like any other circuits, that approach takes time to design, build, and test. Such circuits also need a lot of room.

In contrast, the MSP430 contains a set of general purpose and application specific circuits, which are in the form of built in peripheral modules. The modules can be directed to behave in the ways we need through the control of a program. The ability to quickly make changes to the program also dramatically reduces product development time. So when using the MSP430, we can save a lot of time, effort, space, and cost. And have some fun during the process.

#### **Purpose of this Book**

The MSP430 is quite literally a remarkable product. It is a computing platform that provides a whole lot of complex data processing capabilities which are abstracted out to a single and far less complex abstract layer in the form of a computer program. We use the program to quickly tailor the processing capabilities to fit our needs.

The modules, especially the peripheral modules, and the ability to program them are the two primary reasons why we choose to use the MSP430 for building products which can monitor and control devices. Therefore, in order to incorporate the MSP430 into a product, knowing about how its modules operate and how to program them to do work are the most important types of knowledge and skills we must develop.

This book has three purposes. The first one is to explain how to write programming instructions which can read and write into the MSP430's registers. The second purpose is to explain the fundamental structure of a program. And the third purpose is to explain how to write programming instructions which prepare the MSP430 for work.

Later volumes will go into far greater detail about individual modules and how to program them.

#### Firmware is the Program of Instructions We Develop for a Microcontroller

The computer program that we develop and load into the microcontroller is also called a firmware program.

Firmware should not be confused with software because of the way they are put into service and used is not the same. And since computer architecture is based upon different levels of abstraction, making a distinction between the two allows us to better explain and design computing systems.

The characteristics which distinguish the two are their installation and runtime behavior. A firmware program is permanently set into the nonvolatile storage fields of memory, and when needed, it is executed directly from those fields. A software program is semi-permanently stored in some type of nonvolatile memory, but when needed, it is loaded into volatile memory and executed from there. When the software program is exited or closed, it is removed from volatile memory.

Arguments can easily be made which dispute these characteristics. But the point here is to have concrete definitions so there will be no confusion about what type of program is begin discussed and so that proper abstractions can be utilized for making explanations and descriptions. For example, such distinctions become important in scenarios where an MSP430 is communicating and interacting with software which is running on conventional personal computers, or local servers, or remote servers. Be aware that Texas Instruments documentation will typically refer to firmware as user software. This book will often refer to the firmware program as just simply the program.

#### Bits, Bytes, and the Native Word are the Basic Units of Data

The binary, decimal, and hexadecimal are positional numbering systems which are used for developing programs. They use a base set of symbols, called numerals or digits, which are combined into a sequence of positions to express a single number of numerical value. Binary numbers are expressed with only two different digits, while decimals use ten different digits, and hexadecimal numbers use sixteen. All use an infinite number of positions, or place values, to express a single number. A binary bit is a single position or place value that represents a single digit. A binary digit can be expressed as either a 0 or 1. The field of computing organizes bits into sets called nibbles, bytes, and words which have a standard quantity of bits.

A nibble is made of four bits, and a byte is made of eight bits. As for the size of a word, the size depends on the microcontroller's central processing unit (CPU), since it works on words of a fixed length, and that length varies from one type of CPU to another. It's called the native word size. Historically, CPU design has progressed through being able to handle four, eight, sixteen, thirty two, and now sixty four bit words.

As will be elaborated upon later, there are two types of words which an MSP430 CPU processes. One type is meant to express the number to an address in memory, and the other type is meant to express the data at the address. When developing a program, we will not be interested in the length of an address number. But we will be interested in the length of data at an address. A single address in MSP430 memory can only store a byte, but the CPU can simultaneously process two bytes at a time. This means that the native word for the MSP430 is sixteen bits wide, or in other words, it is a sixteen bit CPU.

#### How the Microcontroller Views Data

This really depends on where the data appears. When the data is located on the outside of the microcontroller, and it is flowing into or out of a peripheral module, the data will appear as analog or digital voltage signals. The type of signal which actually appears will depend on the peripheral device which is being monitored or controlled. The voltage will typically range from to VDC. And we must take into account that the actual voltage signal produced by the peripheral device may have to be properly conditioned with circuits which act as the interface between the microcontroller and the peripheral device.

The MSP430 does not accept nor produce alternating current (AC) voltage signals. And AC signals must not be confused with analog signals, since AC is typically not used for transporting information. However, for an MSP430 to accept an AC signal, we have to design an interfacing circuit which will convert it to one that fluctuates between zero and 3.6 VDC. And for an MSP430 to produce an AC signal, we have to design a circuit that will convert a direct current voltage signal that fluctuates from

to volts to the appropriate AC voltage signal. But keep in mind that the MSP430 is not intended to be used in that way.

Since the peripheral module acts as a signal interface in between the microprocessor and the peripheral device, it is the point where data under goes conversion. All data which flows from the outside and into the peripheral module is converted by the module to digital data, and vice versa.

Within the microcontroller, the MSP430 microprocessor perceives and handles all data as either bytes or words. However, when developing firmware, our code may

#### 6 Introduction

handle data which is a bit, byte, or word in width. And using firmware to manipulate just a single bit in memory is not uncommon.

#### The MSP430 is Offered with Two Types of Processors: CPU and the CPUX

The MSP430 is offered with two types of CPUs and two sizes of memory. The first type of CPU is just simply called the CPU, and it uses the smaller memory module. The second type of CPU is called the CPUX, and it uses the larger memory module.

The smaller module has addresses of storage, while the larger module has addresses of storage. Both modules provide the same amount of storage at each address in memory; meaning, each address can store only eight bits. The single characteristic which distinguishes the two CPUs is their ability to handle address numbers. The CPUX can handle a larger set of addresses. Other than that, there is no difference between the two CPUs. Also, just because a particular type of CPU may be able to access address of storage, that characteristic does not mean the memory module has that amount of space. The memory module comes in different sizes, depending on the model of MSP430.

#### How We [as Developers] may View and Express Data

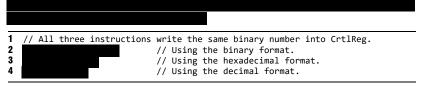

We will be writing code in the C programming language. So from that point of view, meaning, as we view our firmware code while developing it, the data can appear in any valid notation. It can be written as decimal numbers, binary numbers, hexadecimal numbers, or as alphanumerical characters; whichever notation is most convenient and appropriate from our point of view. When loading the program into the microcontroller, the MSP430 C Language Compiler will convert the entire program to machine code, which is expressed in binary form.

Decimal numbers can be used in our firmware code without any special notation. A binary number must be denoted with the prefix the for example, the sum of the for example, the sum of the prefix the for example, the sum of the sum o

When stepping through our code, while our code development tool is in debugging mode, we can configure the tool to present the firmware data, such as numerical variables and constants, to us in binary, decimal, or hexadecimal notation. The instructions to do that are described by a later chapter.

#### Registers are Used for Configuring and Controlling the Microcontroller

The word register has multiple documented origins, which go back to about 1259 of the current epoch, and which are partly borrowed from French (registre) and partly borrowed from Latin (registrum). The undocumented usage most certainly goes back further in time. Its concise meaning varies with context, but it basically means that it is documentation used for recording facts. In the context of an MSP430, here is what it means.

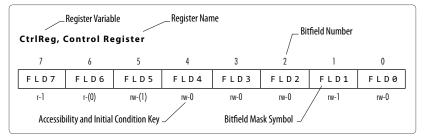

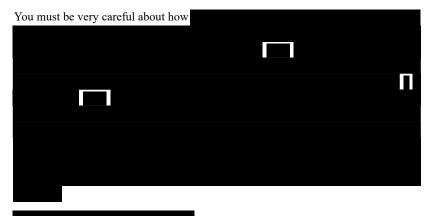

A microcontroller register is a sort of fact storing electronic circuit. It can be defined as having physical characteristics and logical uses. It is physically a set of storage fields where each field can store only a single bit. The storage field is called a bitfield. The bit in a bitfield can be read and manipulated by our firmware.

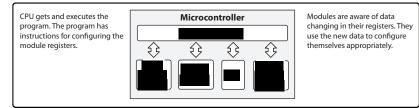

As for its uses, a register has two logical uses. The first use is for putting data into a module, and the second use is for getting data from a module. In other words, from the microprocessor's point of view and our firmware's view, they are data inputs and outputs for modules.

Every module has its own dedicated set of registers. To configure, control, and monitor a module, our firmware must read and write data into their registers. Data which is read from the register is used for making a decision. Data which is written into a register is used for configuring or driving a module. This is the most fundamental concept in programming the MSP430.

The MSP430 has two locations for registers. One is inside of the CPU, and the other is inside of the main memory module.

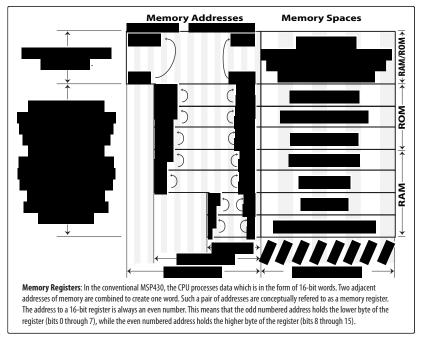

#### **Main Memory Registers**

As will be elaborated upon later, locations in main memory are denoted by address numbers. For the MSP430, the set of address numbers will range from to either

or depending on the CPU type. That set of addresses is called an , and keep in mind that each address can store a single byte of data, and no more.

And up to now, main memory has been referred to as a single memory module, but in reality, it is two modules. One module is made of non-volatile storage technology called read only memory (ROM), and the other is made of volatile storage technology called random access memory (RAM). The latest models of MSP430 are built of ferro-electric RAM (FRAM). When power is removed from the microcontroller, data in the volatile sections of memory is lost, but data is not lost from the nonvolatile sections. The program is stored in the nonvolatile sections of main memory.

Registers which are located in main memory are built of RAM, so when in service, they can be changed by our firmware and the CPU. The quantity of main memory registers is partly dependent on the quantity of modules in the microcontroller, which varies from one model of MSP430 to another. The amount of RAM is also dependent on pricing, meaning that some microcontrollers have more RAM than others in order to accommodate larger amounts of volatile data which our program may create and use.

Registers are typically distributed across the lower addresses in memory. The size of a main memory register will be either **and** or **bits** wide. Do not get the size of a register confused with the fixed size of storage at an address; they are not the same

#### 8 Introduction

thing. Register size is a logical expression of storage space, while address storage size is a physical expression of storage space. This definition will become clearer when you start learning how to use registers.

Many registers are bits wide; therefore, they have a single address. But if the register is bits wide, it's comprised of two adjacent addresses in memory. So technically, those wider registers have a single address is needed for reading and writing into those bit registers. Those technical details will be abstracted away with programming symbols called register variables, as will be explained later.

Since registers are located in the volatile sections of main memory, when the microcontroller starts or restarts, our program will typically have to configure those registers to some extent before the modules can be put into service. To some extent means that most registers will automatically be loaded with default data which may not need to be changed and represents an acceptable or preferred configuration for operating the module. The reset system handles the loading of that data, and it is called system initialization data.

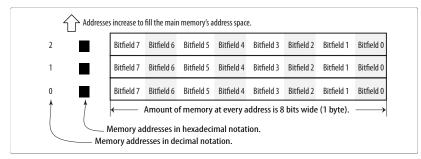

**Diagram 1:** This is the structure of individual storage places in main memory. The first three addresses in memory are shown here. Every address in main memory can store one byte of bits. The lower addresses in main memory are where the registers are located.

#### What is a Main Memory Register used for?

Registers located in main memory are used for setting up, configuring, monitoring, and operating various systems and modules. They provide the means for our program to get and put data into modules. Most registers are completely dedicated to an individual module, while a few are dedicated to handling two or more types of modules.

#### **CPU Registers**

Registers located inside of the CPU are called CPU Registers, and they are sometimes referred to as machine registers. The CPU is built with many registers which have specific purposes, but in the MSP430, only sixteen of them can be accessed with our firmware. And out of those sixteen, we will be concerned with only one of them. It's called the status register.

Fourteen of the CPU registers are built of volatile type storage technology. The remaining two nonvolatile registers are called constant generator registers. The data

9

The status register contains data about the microcontroller's operating state. From a programming perspective, we are mostly concerned with the status register bitfields which control the clock module and which can block CPU interruption signals, also called interrupt requests (IRQ). The clock is used for producing accurate square wave voltage signals which are used by all systems and modules so they can run and be synchronized with each other. As for the interrupt signals, they ask the CPU to stop what it's doing and execute a specific instruction in our program called an interrupt service routine (ISR). Requests from some modules can be blocked by manipulating a specific bit in the status register.

And finally, except for the constant generator register and status register, the CPU registers are designed to accommodate the width of any address number in the memory module. Since these registers handle the addresses to data, and not the actual data itself. For an MSP430 which is built of the conventional MSP430 CPU, it must be able to access an address space having address numbers ranging from to bits in width, while CPUX be able to access a space which reaches up to bit address numbers.

Other types of CPU registers, which are of no immediate concern to us as beginners, will handle the actual data and manipulate it, based upon our program's instructions. After we become more experienced with developing firmware, those unoccupied CPU registers can be utilized for storing data which can be accessed very quickly.

#### Summary

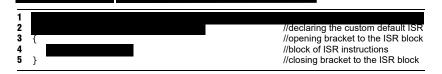

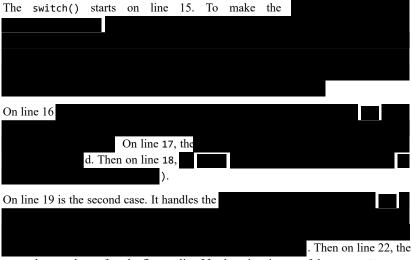

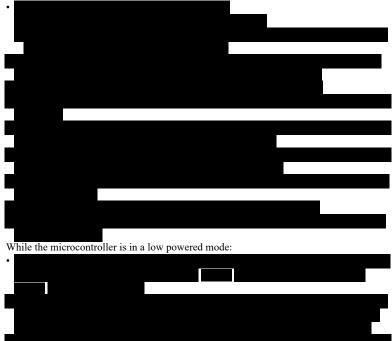

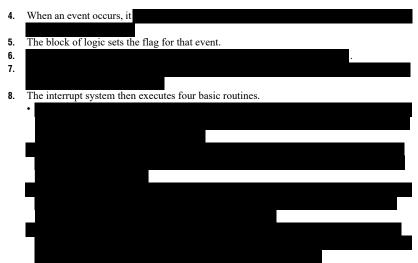

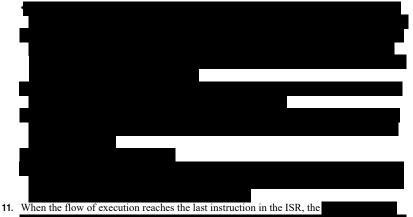

Data can be understood as electrical signals and binary numbers. When entering and leaving the microcontroller, they are in the form of analog and digital electrical signals. When they are inside of the microcontroller, they are in the form of binary numbers so the CPU can process them.